RISC-V: Transforming the Global Technology Landscape

RISC-V, an open-standard Instruction Set Architecture (ISA) initiated at UC Berkeley in 2010, is reshaping the global semiconductor industry. Unlike proprietary ISAs like ARM or x86, RISC-V is royalty-free and open-source, offered under permissive licenses such as Creative Commons and BSD. This accessibility democratizes processor design, enabling developers, startups, and nations to create custom microprocessors without exorbitant licensing costs. With a modular and extensible design, RISC-V supports applications from low-power microcontrollers to high-performance AI accelerators, fostering innovation across industries like IoT, automotive, and space.

The global RISC-V community, spanning over 70 countries and nearly 4,000 members, drives collaborative development through RISC-V International, a Swiss non-profit. Its impact is evident in projects like India’s SHAKTI processor by IIT Madras and China’s XiangShan cores, which rival ARM Cortex-A76 performance. By reducing dependency on proprietary technologies, RISC-V empowers indigenous initiatives, aligning with self-reliance goals like India’s “Make in India” strategy.

RISC-V and Indigenous Projects: The C-DAC VEGA Program

India’s Centre for Development of Advanced Computing (C-DAC), under the Ministry of Electronics and Information Technology (MeitY), leverages RISC-V to develop indigenous microprocessors through the Digital India RISC-V (DIR-V) program. The VEGA Microprocessor initiative has produced a portfolio of RISC-V-based processors, including the THEJAS32 and THEJAS64 System-on-Chips (SoCs). These efforts support India’s “Atmanirbhar Bharat” vision, reducing reliance on imported semiconductors and fostering a domestic hardware ecosystem.

C-DAC’s VEGA series includes development boards like Aries V2, Aries Micro V1, Aries IoT V2, Aries Dot V1, Aries Alpha V1, Aries Nova V1, and the flagship Aries V3. These platforms target applications from basic embedded systems to IoT and wearables, showcasing the versatility of RISC-V. The open-source nature of RISC-V allows C-DAC to customize processors for specific needs, such as India’s defense and space sectors, while accelerating development through community-driven tools and resources.

Aries V3: High-Level Specifications

The Aries V3 board, powered by the THEJAS32 SoC, is a cornerstone of C-DAC’s VEGA portfolio. Designed for embedded systems and microcontroller programming, it offers a robust platform for developers. Key specifications include:

- Processor: THEJAS32 SoC with a single-core VEGA ET1031, a 32-bit RISC-V (RV32IM) processor operating at 100 MHz.

- Memory: 256 KB internal SRAM, 2 MB external SPI flash memory.

- Peripherals:

- 3 UARTs, 4 SPIs, 3 I2C interfaces.

- 8 PWM channels, 3 timers, 32 GPIOs.

- Connectivity: USB-C for programming and debugging, compatible with CP2102 USB-to-serial chip.

- Power: USB-C or 7-12V DC input for standalone operation.

- Form Factor: Arduino Uno-compatible pinout with additional headers for extended GPIO access.

The Aries V3 supports the VEGA Software Development Kit (SDK) with a RISC-V GNU Compiler Toolchain and Arduino IDE integration, making it accessible to both novice and experienced developers. Its compact design and rich peripheral set make it ideal for IoT, sensor networks, and control systems.

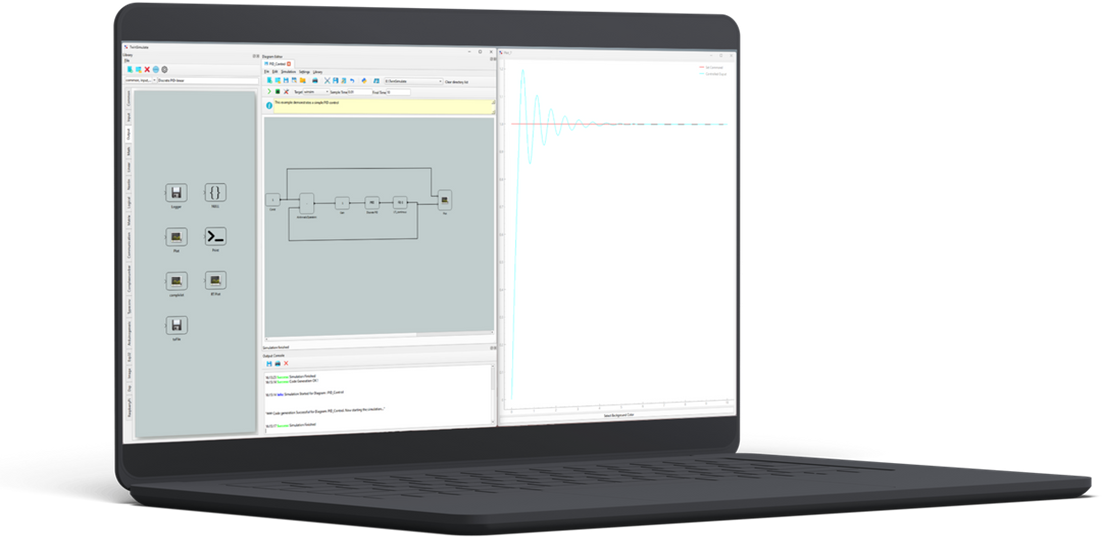

TwinSimulate: Revolutionizing Development with Model-Based Design

TwinSimulate, developed by Vista1labs, is a model-based digital twin platform that also provides automatic code generation capability . As the first tool of its kind to support the VEGA THEJAS32 processor, TwinSimulate enables developers to create graphical system models, simulate behavior, and automatically generate optimized C/C++ code for the Aries V3. This approach significantly accelerates development, reduces errors, and enhances accessibility for developers unfamiliar with RISC-V.

Workflow: From Diagrams to Deployment

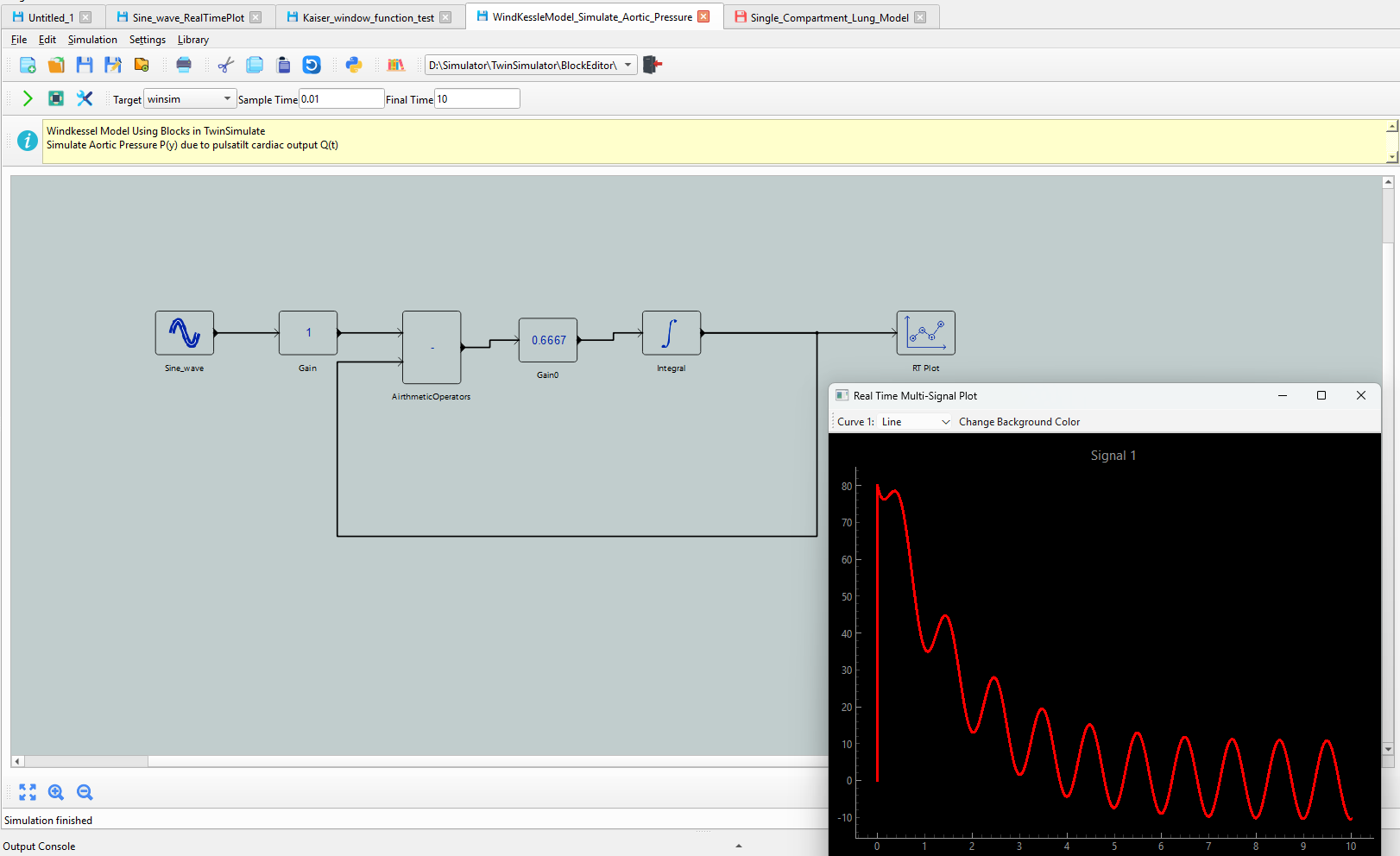

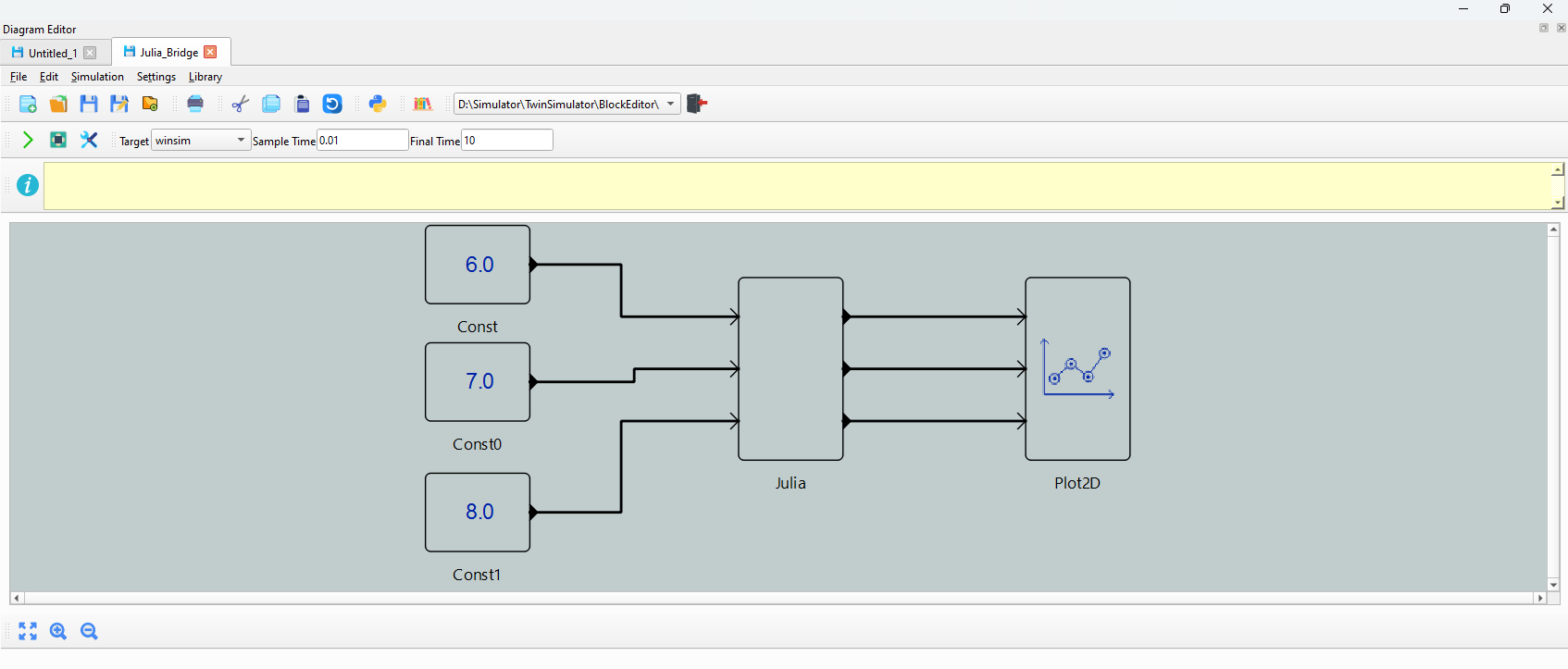

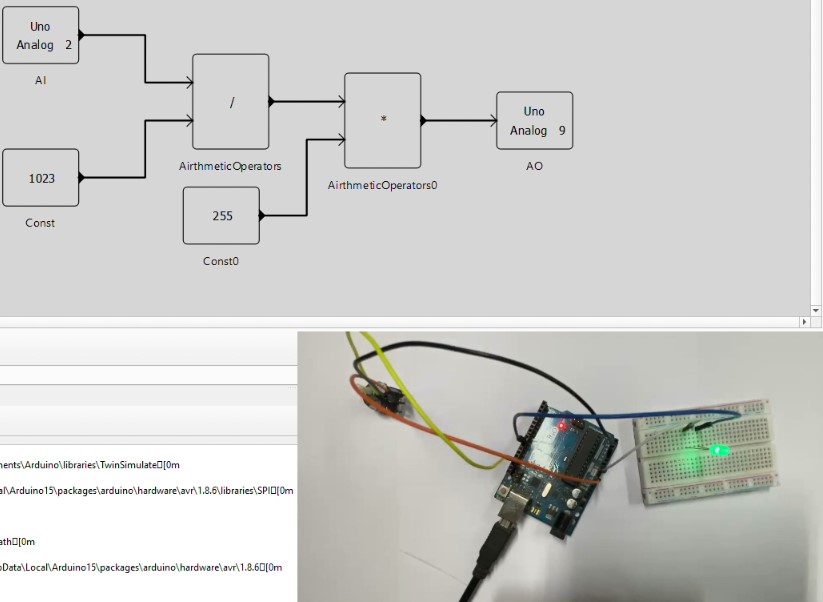

A video demonstration of TwinSimulate’s workflow highlights its seamless transition from design to deployment:

- Graphical Modeling: Developers use a drag-and-drop interface to create block diagrams representing system components (e.g., sensors via I2C, actuators via PWM). These diagrams form a digital twin of the physical system.

- Simulation: The platform simulates the model to validate functionality, allowing developers to test scenarios like sensor failures or control logic without hardware.

- Code Generation: TwinSimulate generates C/C++ code tailored for the THEJAS32, including peripheral drivers and application logic, compatible with the VEGA SDK or Arduino frameworks.

- Deployment: The code is uploaded to the Aries V3 via USB-C, using the board’s UART XMODEM bootloader or Arduino’s programmer. Real-time monitoring via UART enables iterative refinement.

The video showcases how TwinSimulate abstracts low-level programming complexities, enabling rapid prototyping.

There is more that will be shared as we add more interesting examples so stay tuned.

Benefits of TwinSimulate

- Speed: Model-based design cuts development time by up to 50% by automating code generation and eliminating manual driver configuration.

- Reliability: Pre-deployment simulation ensures robust performance, reducing hardware debugging cycles.

- Accessibility: The graphical interface lowers the barrier for novices, fostering adoption in India’s embedded systems community.

- Scalability: Models are reusable across VEGA-based boards, enhancing long-term project efficiency.

Future Prospects

Vista1labs plans to deepen TwinSimulate’s support for the Aries V3 with an expanded library of example models, advanced peripheral blocks, and community-driven contributions. Integration with tools like MATLAB/Simulink and ROS will further enhance its utility. As RISC-V continues to gain traction, the synergy between C-DAC’s Aries V3 and TwinSimulate positions India as a leader in indigenous embedded systems, driving innovation in IoT, automotive, and beyond.

Conclusion

RISC-V’s open-source paradigm is revolutionizing processor design, empowering indigenous projects like C-DAC’s VEGA Microprocessor initiative. The Aries V3, with its versatile THEJAS32 SoC, exemplifies India’s push for self-reliance in semiconductor technology. TwinSimulate’s model-based approach, highlighted in its workflow video, transforms development by enabling rapid, reliable, and accessible design for the Aries V3. Together, these technologies herald a new era of innovation, positioning India at the forefront of the global RISC-V revolution.